ADC-System on the ADMCF32X Application Note (ANF32X ... - Analog Devices

ADC-System on the ADMCF32X Application Note (ANF32X ... - Analog Devices

- Revenir à l'accueil

Farnell Element 14 :

See the trailer for the next exciting episode of The Ben Heck show. Check back on Friday to be among the first to see the exclusive full show on element…

Connect your Raspberry Pi to a breadboard, download some code and create a push-button audio play project.

Puce électronique / Microchip :

Sans fil - Wireless :

Texas instrument :

Ordinateurs :

Logiciels :

Tutoriels :

Autres documentations :

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NA555-NE555-..> 08-Sep-2014 07:33 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD9834-Rev-D..> 08-Sep-2014 07:32 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP430F15x-M..> 08-Sep-2014 07:32 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD736-Rev-I-..> 08-Sep-2014 07:31 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8307-Data-..> 08-Sep-2014 07:30 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Single-Chip-..> 08-Sep-2014 07:30 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Quadruple-2-..> 08-Sep-2014 07:29 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADE7758-Rev-..> 08-Sep-2014 07:28 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX3221-Rev-..> 08-Sep-2014 07:28 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB-to-Seria..> 08-Sep-2014 07:27 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8313-Analo..> 08-Sep-2014 07:26 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54HC164-SN..> 08-Sep-2014 07:25 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8310-Analo..> 08-Sep-2014 07:24 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8361-Rev-D..> 08-Sep-2014 07:23 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2N3906-Fairc..> 08-Sep-2014 07:22 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD584-Rev-C-..> 08-Sep-2014 07:20 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADE7753-Rev-..> 08-Sep-2014 07:20 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TLV320AIC23B..> 08-Sep-2014 07:18 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD586BRZ-Ana..> 08-Sep-2014 07:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STM32F405xxS..> 27-Aug-2014 18:27 1.8M

Farnell-MSP430-Hardw..> 29-Jul-2014 10:36 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM324-Texas-..> 29-Jul-2014 10:32 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM386-Low-Vo..> 29-Jul-2014 10:32 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NE5532-Texas..> 29-Jul-2014 10:32 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Hex-Inverter..> 29-Jul-2014 10:31 875K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AT90USBKey-H..> 29-Jul-2014 10:31 902K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AT89C5131-Ha..> 29-Jul-2014 10:31 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP-EXP430F5..> 29-Jul-2014 10:31 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Explorer-16-..> 29-Jul-2014 10:31 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMP006EVM-Us..> 29-Jul-2014 10:30 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Gertboard-Us..> 29-Jul-2014 10:30 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMP91051-Use..> 29-Jul-2014 10:30 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Thermometre-..> 29-Jul-2014 10:30 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-user-manuel-..> 29-Jul-2014 10:29 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-fx-3650P-fx-..> 29-Jul-2014 10:29 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2-GBPS-Diffe..> 28-Jul-2014 17:42 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMT88-2.4V-1..> 28-Jul-2014 17:42 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Octal-Genera..> 28-Jul-2014 17:42 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Dual-MOSFET-..> 28-Jul-2014 17:41 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TLV320AIC325..> 28-Jul-2014 17:41 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54LV4053A-..> 28-Jul-2014 17:20 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TAS1020B-USB..> 28-Jul-2014 17:19 6.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TPS40060-Wid..> 28-Jul-2014 17:19 6.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TL082-Wide-B..> 28-Jul-2014 17:16 6.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RF-short-tra..> 28-Jul-2014 17:16 6.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-maxim-integr..> 28-Jul-2014 17:14 6.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TSV6390-TSV6..> 28-Jul-2014 17:14 6.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fast-Charge-..> 28-Jul-2014 17:12 6.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NVE-datashee..> 28-Jul-2014 17:12 6.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Excalibur-Hi..> 28-Jul-2014 17:10 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Excalibur-Hi..> 28-Jul-2014 17:10 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-REF102-10V-P..> 28-Jul-2014 17:09 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMS320F28055..> 28-Jul-2014 17:09 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MULTICOMP-Ra..> 22-Jul-2014 12:35 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RASPBERRY-PI..> 22-Jul-2014 12:35 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Dremel-Exper..> 22-Jul-2014 12:34 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STM32F103x8-..> 22-Jul-2014 12:33 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BD6xxx-PDF.htm 22-Jul-2014 12:33 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L78S-STMicro..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RaspiCam-Doc..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB520-SB5100..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-iServer-Micr..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUMINARY-MIC..> 22-Jul-2014 12:31 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEXAS-INSTRU..> 22-Jul-2014 12:31 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEXAS-INSTRU..> 22-Jul-2014 12:30 4.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CLASS 1-or-2..> 22-Jul-2014 12:30 4.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEXAS-INSTRU..> 22-Jul-2014 12:29 4.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Evaluating-t..> 22-Jul-2014 12:28 4.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM3S6952-Mic..> 22-Jul-2014 12:27 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Keyboard-Mou..> 22-Jul-2014 12:27 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-Full-Datashe..> 15-Jul-2014 17:08 951K

Farnell-Full-Datashe..> 15-Jul-2014 17:08 951K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-pmbta13_pmbt..> 15-Jul-2014 17:06 959K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EE-SPX303N-4..> 15-Jul-2014 17:06 969K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-NX..> 15-Jul-2014 17:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MIDAS-un-tra..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SERIAL-TFT-M..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCOC1-Farnel..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-series..> 15-Jul-2014 16:48 787K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-DC-Conver..> 15-Jul-2014 16:48 781K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 16:47 803K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMLM-Series-..> 15-Jul-2014 16:47 810K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEL-5-Series..> 15-Jul-2014 16:47 814K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TXL-series-t..> 15-Jul-2014 16:47 829K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEP-150WI-Se..> 15-Jul-2014 16:47 837K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AC-DC-Power-..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-Instruct..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TOS-tracopow..> 15-Jul-2014 16:47 852K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TCL-DC-traco..> 15-Jul-2014 16:46 858K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-series-t..> 15-Jul-2014 16:46 875K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-Series..> 15-Jul-2014 16:46 897K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-3-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEN-8-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 16:46 947K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HIP4081A-Int..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ISL6251-ISL6..> 07-Jul-2014 19:47 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DG411-DG412-..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3367-ARALDIT..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ICM7228-Inte..> 07-Jul-2014 19:46 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-K..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Silica-Gel-M..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TKC2-Dusters..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CRC-HANDCLEA..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-760G-French-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Decapant-KF-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1734-ARALDIT..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Araldite-Fus..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-fiche-de-don..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-safety-data-..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-4-Hardener..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC-Debugger-..> 07-Jul-2014 19:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP430-Hardw..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SmartRF06-Ev..> 07-Jul-2014 19:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2531-USB-H..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK889B-PONT-..> 07-Jul-2014 19:42 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-User-Guide-M..> 07-Jul-2014 19:41 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-T672-3000-Se..> 07-Jul-2014 19:41 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-0050375063-D..> 18-Jul-2014 17:03 2.5M

Farnell-0050375063-D..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mini-Fit-Jr-..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-43031-0002-M..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0433751001-D..> 18-Jul-2014 17:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cube-3D-Prin..> 18-Jul-2014 17:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MTX-Compact-..> 18-Jul-2014 17:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MTX-3250-MTX..> 18-Jul-2014 17:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 18-Jul-2014 17:00 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCP3421-Micr..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM19-Texas-I..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-S..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMH6518-Texa..> 18-Jul-2014 16:59 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD7719-Low-V..> 18-Jul-2014 16:59 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DAC8143-Data..> 18-Jul-2014 16:59 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BGA7124-400-..> 18-Jul-2014 16:59 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SICK-OPTIC-E..> 18-Jul-2014 16:58 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT3757-Linea..> 18-Jul-2014 16:58 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT1961-Linea..> 18-Jul-2014 16:58 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2420-2..> 18-Jul-2014 16:57 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DS3231-DS-PD..> 18-Jul-2014 16:57 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RDS-80-PDF.htm 18-Jul-2014 16:57 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8300-Data-..> 18-Jul-2014 16:56 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT6233-Linea..> 18-Jul-2014 16:56 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX1365-MAX1..> 18-Jul-2014 16:56 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPSAF5130-PD..> 18-Jul-2014 16:56 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DP83846A-DsP..> 18-Jul-2014 16:55 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Dremel-Exper..> 18-Jul-2014 16:55 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCOC1-Farnel..> 16-Jul-2014 09:04 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S1203_121..> 16-Jul-2014 09:04 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PN512-Full-N..> 16-Jul-2014 09:03 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S4011_402..> 16-Jul-2014 09:03 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC408x-7x 3..> 16-Jul-2014 09:03 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PCF8574-PCF8..> 16-Jul-2014 09:03 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC81xM-32-b..> 16-Jul-2014 09:02 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC1769-68-6..> 16-Jul-2014 09:02 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC3220-30-4..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC11U3x-32-..> 16-Jul-2014 09:01 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3ICS1002-1..> 16-Jul-2014 09:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-T672-3000-Se..> 08-Jul-2014 18:59 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-tesa®pack63..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Encodeur-USB..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2530ZDK-Us..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2020-Manuel-..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Synchronous-..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Arithmetic-L..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NA555-NE555-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-4-Bit-Magnit..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM555-Timer-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L293d-Texas-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54HC244-SN..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX232-MAX23..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-High-precisi..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMU-Instrume..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-900-Series-B..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BA-Series-Oh..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-270-Series-O..> 08-Jul-2014 18:49 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tiva-C-Serie..> 08-Jul-2014 18:49 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTO-Souriau-..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Clipper-Seri..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOURIAU-Cont..> 08-Jul-2014 18:47 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-851-Series-P..> 08-Jul-2014 18:47 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-SL59830-Inte..> 06-Jul-2014 10:07 1.0M

Farnell-SL59830-Inte..> 06-Jul-2014 10:07 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1210-PDF.htm 06-Jul-2014 10:06 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD7171-16-Bi..> 06-Jul-2014 10:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-Noise-24..> 06-Jul-2014 10:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:05 938K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74LCX573-Fai..> 06-Jul-2014 10:05 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1N4148WS-Fai..> 06-Jul-2014 10:04 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FAN6756-Fair..> 06-Jul-2014 10:04 850K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 06-Jul-2014 10:04 861K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES1F-ES1J-fi..> 06-Jul-2014 10:04 867K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-QRE1113-Fair..> 06-Jul-2014 10:03 879K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2N7002DW-Fai..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDC2512-Fair..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDV301N-Digi..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S1A-Fairchil..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BAV99-Fairch..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74AC00-74ACT..> 06-Jul-2014 10:03 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NaPiOn-Panas..> 06-Jul-2014 10:02 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LQ-RELAYS-AL..> 06-Jul-2014 10:02 924K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ev-relays-ae..> 06-Jul-2014 10:02 926K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:02 931K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplifier-In..> 06-Jul-2014 10:02 940K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serial-File-..> 06-Jul-2014 10:02 941K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Both-the-Del..> 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Videk-PDF.htm 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 04-Jul-2014 10:43 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Sensorless-C..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-197.31-KB-Te..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F609-61..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PADO-semi-au..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-03-iec-runds..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ACC-Silicone..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-TDS10..> 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-03-iec-runds..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0430300011-D..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-06-6544-8-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-Polyimide..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-VolitionT..> 25-Mar-2014 08:18 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10BQ060-PDF.htm 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10TPB47M-End..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-12mm-Size-In..> 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-24AA024-24LC..> 23-Jun-2014 10:26 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-50A-High-Pow..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-197.31-KB-Te..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1907-2006-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-5910-PDF.htm 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-6517b-Electr..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-True-Syste..> 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ACC-Silicone..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD524-PDF.htm 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADL6507-PDF.htm 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADSP-21362-A..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1210-PDF.htm 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1225-12-V..> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF2412-24-V..> 01-Apr-2014 07:39 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AN10361-Phil..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARADUR-HY-13..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-201..> 21-Mar-2014 08:12 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-CW-..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 19-Mar-2014 18:04 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 11-Mar-2014 07:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega640-VA..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny20-PDF..> 25-Mar-2014 08:19 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 01-Apr-2014 07:42 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplificateu..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-An-Improved-..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ATmega..> 19-Mar-2014 18:03 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Avvertenze-e..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC846DS-NXP-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC847DS-NXP-..> 23-Jun-2014 10:24 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BF545A-BF545..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK2650A-BK26..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BT151-650R-N..> 13-Jun-2014 18:40 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BTA204-800C-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BUJD203AX-NX..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV29F-600-N..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV79E-serie..> 10-Mar-2014 16:19 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BZX384-serie..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Battery-GBA-..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A-6150-C.A..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A 8332B-C...> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2560-Bluet..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CD4536B-Type..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CIRRUS-LOGIC..> 10-Mar-2014 17:20 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CS5532-34-BS..> 01-Apr-2014 07:39 3.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cannon-ZD-PD..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ceramic-tran..> 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cles-electro..> 21-Mar-2014 08:13 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Conception-d..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Connectors-N..> 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Construction..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Controle-de-..> 11-Mar-2014 08:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cordless-dri..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:51 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Davum-TMC-PD..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-De-la-puissa..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Directive-re..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Documentatio..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ECO-Series-T..> 20-Mar-2014 08:14 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ELMA-PDF.htm 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EMC1182-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 04-Jul-2014 10:43 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-Sample..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES2333-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ed.081002-DA..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F28069-Picco..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F42202-PDF.htm 19-Mar-2014 18:00 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDS-ITW-Spra..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FICHE-DE-DON..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fastrack-Sup..> 23-Jun-2014 10:25 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ferric-Chlor..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fluke-1730-E..> 14-Jun-2014 18:23 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-A-FROI..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-MAT-Re..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GN-RELAYS-AG..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HC49-4H-Crys..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HFE1600-Data..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HI-70300-Sol..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HUNTSMAN-Adv..> 10-Mar-2014 16:17 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Haute-vitess..> 11-Mar-2014 08:17 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-IP4252CZ16-8..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Instructions..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-KSZ8851SNL-S..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L-efficacite..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LCW-CQ7P.CC-..> 25-Mar-2014 08:19 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LME49725-Pow..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-542-..> 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-3463..> 25-Mar-2014 08:19 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUXEON-Guide..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Leaded-Trans..> 23-Jun-2014 10:26 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Les-derniers..> 11-Mar-2014 07:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Loctite3455-..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-cost-Enc..> 13-Jun-2014 18:42 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Lubrifiant-a..> 26-Mar-2014 18:00 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC3510-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC21605-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCF532x-7x-E..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICREL-KSZ88..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICROCHIP-PI..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-39-00-..> 10-Mar-2014 17:19 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43020-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43160-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-87439-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MPXV7002-Rev..> 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MX670-MX675-..> 14-Jun-2014 09:46 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microchip-MC..> 13-Jun-2014 18:27 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microship-PI..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-Active..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-MCCOG4..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Miniature-Ci..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mistral-PDF.htm 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-83421-..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-COMMER..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-Crimp-..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Multi-Functi..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NTE_SEMICOND..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-74VHC126..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-BT136-60..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PBSS9110..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PCA9555 ..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PMBFJ620..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN1R7-..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN7R0-..> 10-Mar-2014 17:19 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-TEA1703T..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Nilï¬-sk-E-..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Novembre-201..> 20-Mar-2014 17:38 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-Master..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OSLON-SSL-Ce..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OXPCIE958-FB..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PADO-semi-au..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5160T-60..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTA143X-ser..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTB123TT-NX..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD5V0F1BL-..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD9X5.0L-P..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F609-61..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2455-2..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC24FJ256GB..> 14-Jun-2014 09:51 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT3906-PNP..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT4403-PNP..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4002EL-N..> 14-Jun-2014 18:18 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4010CEH-..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-15..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EC..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EZ..> 20-Mar-2014 08:10 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Id..> 20-Mar-2014 17:35 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ne..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ra..> 20-Mar-2014 17:37 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-TS..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Y3..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pico-Spox-Wi..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pompes-Charg..> 24-Apr-2014 20:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ponts-RLC-po..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Portable-Ana..> 29-Mar-2014 11:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Premier-Farn..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Produit-3430..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Proskit-SS-3..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Puissance-ut..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Q48-PDF.htm 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Radial-Lead-..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Realiser-un-..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Reglement-RE..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Repartiteurs..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S-TRI-SWT860..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB175-Connec..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMBJ-Transil..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOT-23-Multi..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SPLC780A1-16..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SSC7102-Micr..> 23-Jun-2014 10:25 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SVPE-series-..> 14-Jun-2014 18:15 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Sensorless-C..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Septembre-20..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-PicoSc..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-Standa..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-2600B..> 20-Mar-2014 17:30 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-TDS10..> 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Signal-PCB-R..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Strangkuhlko..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Supercapacit..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TDK-Lambda-H..> 14-Jun-2014 18:21 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEKTRONIX-DP..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tektronix-AC..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Telemetres-l..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Termometros-..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-The-essentia..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-U2270B-PDF.htm 14-Jun-2014 18:15 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB-Buccanee..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB1T11A-PDF..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-V4N-PDF.htm 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-WetTantalum-..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-AC-Octop..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-MC16-XPS..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-YAGEO-DATA-S..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ZigBee-ou-le..> 11-Mar-2014 07:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-celpac-SUL84..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-china_rohs_o..> 21-Mar-2014 10:04 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:35 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ir1150s_fr.p..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-manual-bus-p..> 10-Mar-2014 16:29 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-propose-plus..> 11-Mar-2014 08:19 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-techfirst_se..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-205-20..> 20-Mar-2014 17:37 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-470-Fo..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-uC-OS-III-Br..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-7866HD.pdf-PD..> 29-Mar-2014 11:46 472K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_ENREGISTR..> 29-Mar-2014 11:46 461K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_MESUREURS..> 29-Mar-2014 11:46 435K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 481K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 442K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 422K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-SP270.pdf-PDF..> 29-Mar-2014 11:46 464K

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 1 of 17

a

ADC-System on the ADMCF32X

ANF32X-05

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 2 of 17

Table of Contents

SUMMARY...................................................................................................................... 3

1 ADC-SYSTEM – SINGLE SLOPE............................................................................ 3

1.1 Single Slope Converter of the ADMCF32X..................................................................................................3

1.2 Choosing the Timing Capacitor Value .........................................................................................................4

1.3 Different capacitors ........................................................................................................................................5

1.4 Resolution........................................................................................................................................................5

1.5 Current trimming of the internal current source. .......................................................................................5

1.5.1 Calibrating the current source. .....................................................................................................................6

1.6 ADC – Auto-calibration .................................................................................................................................7

1.6.1 Example – Calculations................................................................................................................................8

1.6.2 Correct reading.............................................................................................................................................9

2 THE ADCF32X LIBRARY ROUTINES................................................................... 10

2.1 Using the ADC routines ...............................................................................................................................10

2.2 Configuring the ADC block: ADC_Init;.....................................................................................................11

2.3 Configuring the Autocalibration block: AutoCal_INIT; ..........................................................................11

2.4 Running the Autocalibration routine; ADC_Calibrate; ...........................................................................11

2.5 Reading from the ADC: ADC_Set_AUXch(X) & ReadADC(ADCX); ....................................................14

3 SOFTWARE EXAMPLE: ADC INPUT TO GENERATE PWM............................... 15

3.1 The main program: Main.dsp .....................................................................................................................15

3.2 The main include file: main.h ......................................................................................................................17

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 3 of 17

Summary

This application note describes how the 6 channel single slope ADC system on the ADMCF32X DSP

based motor controller operates and how to utilize this system.

In many standard drive systems in the low-end range, the need for high resolution ADC-systems is not a

requirement. In these cases, a simple topology for analog data-acquisition system (single-slope) can be

implemented to combine the ADC-system directly with the DSP. In that way a low-cost system can be

implemented by the use of only one single low-cost processor.

1 ADC-system – Single Slope

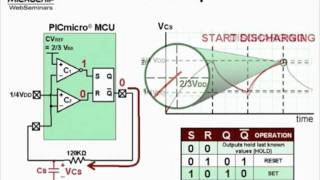

The ADC-system of the ADMCF32X is based upon a 6-channel single slope Analog Data Acquisition

topology, with a resolution of 12-bit. This topology converts data by simply timing the crossover between

the analog input and a sawtooth reference (see Figure 2).

1.1 Single Slope Converter of the ADMCF32X

The Single slope system is a 7-channel ADC-system where four of the channels are multiplexed into a 4-1

MUX. The fourth channel is used for internal voltage reference. The first three AD-converters V1, V2

and V3 are dedicated converters used to measure for example: two phase-currents and one phase-voltage

in a closed loop control system. The four remaining ADC’s are multiplexed into the last comparator and

thereby only updated slower than the dedicated channels. These ADCs are perfect for

Figure 1 – Block-diagram of the single slope ADC-system

measuring slower feedback signals for the controller. The selected analog input through the multiplexer is

determined by using bits 0 and 1 in the MODECTRL register1.

1 For further details see “ Single Chip DSP Motor Controller – ADMCF32X”, Datasheet, Analog Devices

Inc.,

Isense amplification

only on ADMCF328

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 4 of 17

The analog to digital conversion is performed in a precise and simple manner. A reference ramp is

generated by charging the external capacitor, C, with a programmable current source ICONST_TRIM (3

Bit - see Figure 1). For synchronization to the PWM, the timing is locked to the PWMSYNC pulses.

Every time a new PWMSYNC pulse is generated a reset of the voltage across the capacitor is applied, see

Figure 2. The current source ICONST_TRIM is generated within the ADMCF32X and made available at

the dedicated ICONST pin.

The timing-block of the ADC-system consists of a 12-bit counter clocked at a frequency that is either

equal to the DSP clock rate (CLKOUT) or half the DSP clock rate (CLKIN). For the ADCMF32X the

maximum CLKOUT rate is 20 MHz (50 ns period) and the maximum CLKIN rate is 10 MHz (100 ns).

Counter reset is done during a high PWMSYNC pulse at the start of each PWM cycle, so that the

operation of the ADC is intrinsically linked to the PWM generation unit. When the output of the

comparator (ADC1- ADCAUX) goes high the value of the counter is latched into the corresponding 12-

bit ADC-register. These values are loaded into output-registers after the first PWMSYNC-interrupt has

occurred, but a real value is first available after the second PWMSYNC- interrupt.

Figure 2 - Timing of the A/D Conversion on the ADMCF32X

In the case of over-voltage; the analog input-voltage exceeds the timing ramp voltage in the ADC-system,

the comparator output will be continually low and the value placed in the ADC-register will be 0xFFF0 –

indicating overflow.

1.2 Choosing the Timing Capacitor Value

The reference voltage saw-tooth is based on the PWM-period, the capacitor and the value of the current

source. The maximum value of the voltage, (see Figure 2) can be calculated as:

NOM

CONST_TRIM PWM CRST

c,max C

I (T T )

V

−

= [1]

Where

ICONST_TRIM : the current source – With ICONST_TRIM = 0 typically !100 μA.

TPWM : the PWM-Switching period. TPWM is equal to the switching period in single update mode

and the half in double update mode.

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 5 of 17

TCRST : Programmable from 0.05μs to 12.5μs – default value ! 2μs.

CNOM : The selected value for the timing capacitor.

For minimum desired reference voltage about 3.5 V the capacitor to maintain full linearity across the

ADC operating range can be calculated on assumption of. In this case taking a variation of ± 10 %, on the

current-source and timing-capacitor into account the capacitor can be calculated under worst case

conditions as:

(1.1)(3.5)

(0.9*I )(T T )

C CONST PWM CRST

NOM

= − [2]

Choosing for examples a 20kHz switching frequency (Single update mode) resolves in a nominal

capacitor CNOM at 1.12 nF. (Choice of analytical capacitor ≈ 1.2 nF)2. This choice is with the giver 20kHz

switching frequency the first match for the selected capacitor.

1.3 Different capacitors

To ensure the linearity of the converter the need of a “linear” capacitance over voltage - as small leakage

as possible is needed. For that reason the capacitor choice for optimal interface with the ADMC part is

either polycarbonate, polyphenylene or metallised polyester film capacitors. Of course the choice of any

given capacitor depends on the cost and the given tolerance, which match the complete design.

1.4 Resolution

Since the ADC-system is internally linked to the PWM-system, the effective resolution of the ADC will

directly be a function of the PWM switching frequency. The resolution of the ADC is determined by the

rate at which the ADC-counter is locked (As already discussed – bit 7 in the MODECTRL-register).

The formula for calculating the maximum count (MaxCount) of the ADC becomes:

, MODECTRL(7) 1

t

(T T )

MaxCount

CK

= PWM − CRST = [3]

, MODECTRL(7) 0

t *2

(T T )

MaxCount

CK

= PWM − CRST = [4]

Again we can assume a counter clock at the DSP CLKOUT frequency and a TCRST at 2μs – with a 20 kHz

PWM frequency the maximum count can be calculated to 960 which gives a resolution of around 10-Bit3.

1.5 Current trimming of the internal current source.

As already mentioned the structure of the converter is based upon the voltage over an external capacitor.

The magnitude of the current source can depend on manufacturing change from part to part. To overcome

this difference along with the variation on the external capacitor, the internal current source is made

programmable. This means that the output of the current source always can be trimmed to within 5% of

the 100μA target source. A 3-BIT register ICONST_TRIM allows the user to make this adjustment.

2 This is trimmeble depending on the chosen switching frequency.

3 In the “Single Chip DSP Motor Controller – ADMCF32X” Data-sheet, different calculations of the

resolution is made (Table VII).

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 6 of 17

As can be seen on Figure 3, this tuning allows the user to optimize the chosen capacitor. With the 3-BIT

register that varies the output from minimum ICONST_TRIM(0x0) to Maximum ICONST_TRIM(0x7).

Figure 3 - Timing capacitor selection

1.5.1 Calibrating the current source.

With a definition of a desired ramp of about 3.5V the ramp should be as close as possible to these 3.5V.

One way of doing this is by using the internal 2.5V reference and comparing it to the mathematical

calculated target value. If the target value is not reached increment the value in the ICONST_TRIM

register. Continue on this calibration until the target value is reached. If the capacitor is not chosen

correctly it interferes directly with the slope of the reference voltage delivered by the capacitor. In the

case illustrated in Figure 4 two cases illustrate the problems with the slope generation. In the top-case the

Figure 4 - Different slopes for the converter

chosen capacitor for the converter is to big in comparison with the chosen frequency. Even after a tuning

(higher current-flow in the capacitor) the slope never reaches the target-ramp. In this case the converter

returns with 0xFFF – Which is not a valid value. On the other hand – the lower plot – The capacitor is to

small with the same choice of frequency. Here again the converter will return values that are not in the

correct range. If the converter is proper tuned (right capacitor for the chosen frequency) the slope will

look something like expressed at Figure 2 where Vmax is the 3.5V

Capacitor much to

SMALL for the

selected frequency

Capacitor much to

BIG for the selected

frequency

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 7 of 17

1.6 ADC – Auto-calibration

The accuracy of the single slope converter depends on the voltage ramp by the external capacitor and the

internal current-source as explained in section 1.5. In mass production the variation on these capacitors

can easily vary within a few percent. As already talked though the current calibration of the internal

current source can be used to trim the level of voltage on the converter. However, it can in most cases also

be an advantage to ad a SW ramp calibration depending on the resulting slope of the converter.

A piece of software is made to optimize the use of the ADC. The optimization is done on the basis of a

one-point calibration on the ADC, from which the maximum number of counts (referring to the maximum

voltage on the charging capacitor) is calculated. The use of the internal reference (2.5V) is used as

reference with the trimming explained in section 1.5. The procedure of the can be seen below:

Auto_Calibrate

Disable all PWM outputs

Calculate target value

for the Converter and

wait for VAUX3 to

stabilize

Select VAUX3 as analog

input and claculate the

conversion time

ADCAUC > Target Value

Increment

ICONST_TRIM and RTI;

If ICONST >= 8

External cap to

big - SET

ERROR-FLAG

YES

NO

At this point the

current source of

the converter is

tuned for

maximum ramp

Autocal_Init

Initialize the

ADC_errrorflag,

start for tuning, delay

and average values

RTS;

At this point all

values are

initialised

RTI;

converter

calibrated

Use the value from

ADCAUX3 (averaged

over 128 samples)

as reference and

calculate the slope

Figure 5 -Flowchart for routine

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 8 of 17

1.6.1 Example – Calculations

As defined though the converter-setup the ADC readings are fixed to channel ADCAUX3 (2.5V).

Reference

Ref

ΔX

ΔY

ADC reading

Desired ADC reading

Figure 6 - Calibrations scheme

Looking at Figure 6 two differences, ΔX and ΔY, are declared. Knowing these two values it is

arithmetical easy to calculate the slope of the system. In this case the counter slope of the ADC-converter

of the ADMC32X. The equations can be expressed as follows:

ADC readings:

ΔY = Reference [5]

Desired ADC readings (converted to hex):

2 ~ 0x5B6D

(3.5)V

(2.5)V

Ref = ⋅ 15 [6]

Here all measured values are scaled to the maximum voltage input – in this module defined from 0 – 3.5

V. This specify that the input to the converter should only be in this range. The ΔX is represented by:

ΔX = Ref [7]

The next step is to calculate the ADC-Slope with the assumed common ADC-offset of the converter to be

zero. This is expressed as:

X

Y

ADCSlope

Δ

= Δ [8]

The maximum number of counts for the ADC-converter can now be calculated by:

MAXCount = ADCSlope⋅DigitalFullScale [9]

where DigitalFullScale = 1 ~ 0x7FFF in 1.15 format.

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 9 of 17

1.6.2 Correct reading

After the auto-calibration sequence is complete, any ADC reading can be corrected for the gain in the

conversion as follows:

ADCSlope

ADCin

ADCCorrected = [10]

Since this correction uses a division operation, which is computationally expensive, it is desirable to rearrange

the equations to only use multiplication and shifts. To make this possible, there is introduced a

value called OneOver_XSlope which is equal to:

( ⋅ X )

=

ADCSlope

1

OneOver_XSlope [11]

The correction can then be re-arranged to use multiplication and shifts only:

ADCCorrected = ADCin ⋅OneOver_XSlope⋅ X [12]

Where

X = 2 Slope_X_Const ; Slope_X_Const is represented in the “Main.h”

Note the extra factor of X in the calculation of OneOver_XSlope and in the calculation of ADCCorrected.

This is necessary since ADCSlope at some frequencies is less than 1/X, making its inverse greater than X.

A typical value of Slope_X_Const is chosen to 3 (X=8) this constant works with frequencies from around

5 to 20 kHz. If the system is taken to other frequencies, a scaling of this constant can in some cases be

necessary.

Furthermore a last checkup is done to ensure no "rollover". If the number is not in specified range it is

kept in between minimum ≈ 0x0000 and maximum ≈ 0x7FFF.

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 10 of 17

2 The ADCF32X Library Routines

2.1 Using the ADC routines

The library provides different routines that configure and initialize the ADC unit on the ADMCF32X. The

ADC routines are developed as an easy-to-use library, which has to be linked to the user’s application.

The objective of this library is for the user to easily get a working system by utilizing this standard

procedure. This package has to be compiled and can then be linked to any application. The user simply

has to include the header files “adcF32X.h” if the ADC on the ADMCF32X has to be used. In

combination with the converter an autocalibration scheme as described in chapter 1.6 has to be used.

Including the “Autocalx.h” and “Autocalx.dsp” files in the users applications code enables furthermore

the functionality of the calibration.

The procedure for compiling and linking will be shown in this example. Macros “ADC_Read(ADCX)4”

are defined for reading the ADC, which can be executed from anywhere in the code. These functions take

care of the scaling and reading of the wanted channel. The read value of the chosen channel is stored in

AR and can now be used in a given application. If the ADCAUX channel are used the choice of channel

has to be enabled before reading the value. This is done by the Macro “ADC_Set_AUXch(X)“ where the

channel is selected. The following table reassumes the set of macros that are defined in this library.

Operation Usage

Configuration of the ADC ADC_Init;

Auto Calibration (with current tune) ADC_Calibrate;

MUX_ADC ADC_Set_AUXch(X);

Read ADC ReadADC(ADCX);

Table 1 Implemented routines for the ADC Block

The four “ADC-files” can be added to the user library for usage in other dedicated programs. The

“ADCF32X.dsp” and the “Autocalx.dsp” files, containing the assembly code for the required calibration

subroutines described in section 1.6. The “ADCF32X.h” and “Autocalx.h” – are header-file where the

functions are declared. The ADC-routine does not require configuration constants, these are declared in

the dedicated ADC modules. For more information about the general structure of the applications notes

and including libraries into user applications refer to "The Library Documentation File"

4 X indicates the wanted channel - ADC1-3 and ADCAUX

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 11 of 17

2.2 Configuring the ADC block: ADC_Init;

The initialization routine ADC_INIT_ initializes the ADC block for standard operation. In this mode the

MODECTRL(7) bit is set to enable the full DSP clockout frequency. The macro Set_Bit_DM is found in

the general-purpose macro file "macro.h".

ADC_INIT_:

Set_Bit_DM(MODECTRL,ADC_COUNTER_SELECT_BIT_OF_MODECTRL); { Set Bit 7 }

RTS;

2.3 Configuring the Autocalibration block: AutoCal_INIT;

The AutoCal_INIT macro sets up the auto calibration block ready for use. By the use of the routine

AutoCal_INIT_ the status and register in the routine are initialized and the AutoCalTask start pointer

enabled.

AutoCal_INIT_:

AR = 0x0;

dm(ADC_ERRORFLAG) = AR;

AR = ^IniTuningIconst;

dm(AutoCalTask) = AR;

AR = Autocal_Delay;

dm(AutoCalCount) = AR;

AR = 0x0;

dm(TempAverage) = AR;

dm(TempAverage+1) = AR;

RTS;

2.4 Running the Autocalibration routine; ADC_Calibrate;

As can be seen from the following code segment, running the ADC_Calibrate macro does not require any

special constants. As talked though in section 1.6 the reference voltage is needed to do the one-point

calibration, this value is calculated in the autocalx.dsp for usage in this internal routine. The only value

needed is the Slope_X_Const already discussed in 1.6.2.

{*******************************************************************************}

{ Library: ADCF32X }

{ file : ADCF32X.dsp }

{ Application Note: Usage of the ADC converter }

{*******************************************************************************}

.CONST Slope_X_Const=3; { Defines a scalingfactor of 8 (2^3)in the ADC-module }

This module calibrates the converter on base of an average measurement of the voltage reference linked to

ADCAUX3. The average counter can be controlled directly by changing the AutoCalAverage constant in the

definition of the Auto calibration file. The Auto calibration is interrupt driven to ensure correct measurement

on the converter, along with more compact coding. The sequence is:

All PWM channels are disconnected using the PWMSEG-register to ensure no signals on the output of the

driver. AUX-channel 3 is selected in the MUX and the target value is calculated on base of PWMSYNCWT

and PWMTM along with the value of the internal reference (2.5V ~ 0x5b6d). To ensure the antialiasing filter

to decay the first value are sampled after 10 interrupts. After this the current calibration of the slope is

performed. Tuning the current source to match the external capacitor with the use of the internal reference.

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 12 of 17

When this is done the slope and thereby the multiplications factor for the converter are determined over an

average of 128 samples on the converter.

IniTuningIconst:

ar=ALLOFF;

dm(PWMSEG)=ar; { IGBT disabled }

ADC_Set_AUXch(3); { Select VAUX3 as analog input }

AY0 = DM(PWMSYNCWT); { Calculate Conversion Time PWMTM-PWMSYNCWT }

AX0 = DM(PWMTM);

AR = AX0 - AY0;

MY0 = 0x5B6D; { Value of 2.5 / 3.5 - 1.15 Format }

MR = AR * MY0(SS); { Result in MR 16.16 format }

Test_Bit_DM(MODECTRL,7); { ADC Counter rate }

SE=0;

if EQ jump SE_0;

SE=1;

SE_0:

SR=ashift MR1 (HI);

SR=SR or lshift MR0 (LO);

DM(Target_Value) = SR1; { Store target value for ramp }

RepeatMeasurement:

AR = ^ExpectMeasureAUXch; { expect one PWM cycle to have in ADCAUX the }

{ value of Vref }

IniTaskAgain:

dm(AutoCalTask) = AR;

RTI;

ExpectMeasureAUXch:

AY0 = dm(AutoCalCount);

AR = AY0 - 1;

dm(AutoCalCount) = AR;

IF GT RTI; { VAUX3 stabilizes in 10 PWM cycles }

AR = AutoCalAverage;

dm(AutoCalCount) = AR;

AR = ^TuningIconst;

JUMP IniTaskAgain;

TuningIconst:

AY0 = DM(Target_Value); { Up / Down on ICONST Current }

AR = DM(ADCAUX);

SR=LSHIFT AR BY -4 (HI); { Due to scaling of the counter }

AR = SR1 - AY0;

IF LT JUMP TuningFinished;

INCREASE:

AR = DM(ICONST_TRIM);

AR = AR + 1;

AF = AR - 0x8;

IF GE JUMP CapacitorLow; { IF ICONST_TRIM>=8 THEN the external }

{ capacitor is too high - Voltage to low }

DM(ICONST_TRIM) = AR;

JUMP RepeatMeasurement;

CapacitorLow:

AR = dm(ADC_ERRORFLAG);

AR = SETBIT 0 OF AR;

dm(ADC_ERRORFLAG) = AR; { it is signaled the error }

AR = ^AutoCal_Ended;

JUMP IniTaskAgain;

TuningFinished:

AR = ^ReadReference;

JUMP IniTaskAgain;

ReadReference:

AY0 = dm(AutoCalCount);

AR = AY0 - 1;

IF LT JUMP SaveReference;

ComputeAverage:

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 13 of 17

dm(AutoCalCount) = AR;

MR1=DM(ADCAUX);

SR=LSHIFT MR1 by -7 (hi);

AY1 = dm(TempAverage);

AY0 = dm(TempAverage+1);

AR = SR0 + AY0;

AX0 = AR, AR = SR1 + AY1 + C;

dm(TempAverage) = AR;

dm(TempAverage+1) = AX0;

RTI;

SaveReference:

AR = dm(TempAverage);

dm(Reference) = AR;

CALL AutoCal_GenerateConstants_;

AR=ALLON;

dm(PWMSEG)=AR;

AR = ^AutoCal_Ended;

dm(AutoCalTask) = AR;

RTI;

As explained in the theory, section 1.6.2, a correct reading of the converter in effectively done without any

division. This implicates that the reciprocal of the converter-slope has to be detected. At some frequencies

(explained earlier) this number becomes bigger than 1 ~ for that reason this code implements the scaling

factor X (Slope_X_Const referring to section 1.6.2 and Main.h).

{********************************************************************************

* *

* Type: Routine *

* *

* Call: call AutoCal_GenerateConstants_; *

* *

AutoCal_GenerateConstants_:

AY1=DM(Reference);

AX0 = 0x5B6D; { Voltage ref: 2.5 Volt ( (2.5)/(3.5)*2^15) }

AY0 = 0x0; { AR =[AY1 AY0]/AX0 }

CALL Div_;

DM(ADCSlope)=AR; { Slope = y/x }

{********************************************************************************

* *

* Type: Routine *

* *

* Call: call Slope_divide; *

* *

Slope_divide:

MR1 = 0x7FFF;

MR0 = 0xFFFF;

SE = -Slope_X_Const;

SR = ASHIFT MR1 (HI);

SR = SR OR LSHIFT MR0 (LO);

AY1 = SR1;

AY0 = SR0;

AX0 = DM(ADCSlope); { Slope }

CALL Div_; { AR = [AY1 AY0]/ AX0 -- 1/2^X/Slope}

DM(Oneover_XSlope)=AR; { Oneover_XSlope}

rts;

.ENDMOD;

a ADC-system on the ADMCF32X ANF32X-05

© Analog Devices Inc., November 2000 Page 14 of 17

2.5 Reading from the ADC: ADC_Set_AUXch(X) & ReadADC(ADCX);

These two macros select and read the wanted channel on the converter. From the Current Calibration

routine the values of the slope is detected. This value is used to scale the input values on the selected